2115 words

11 minutes

主频和时钟配置

一、时钟图详解

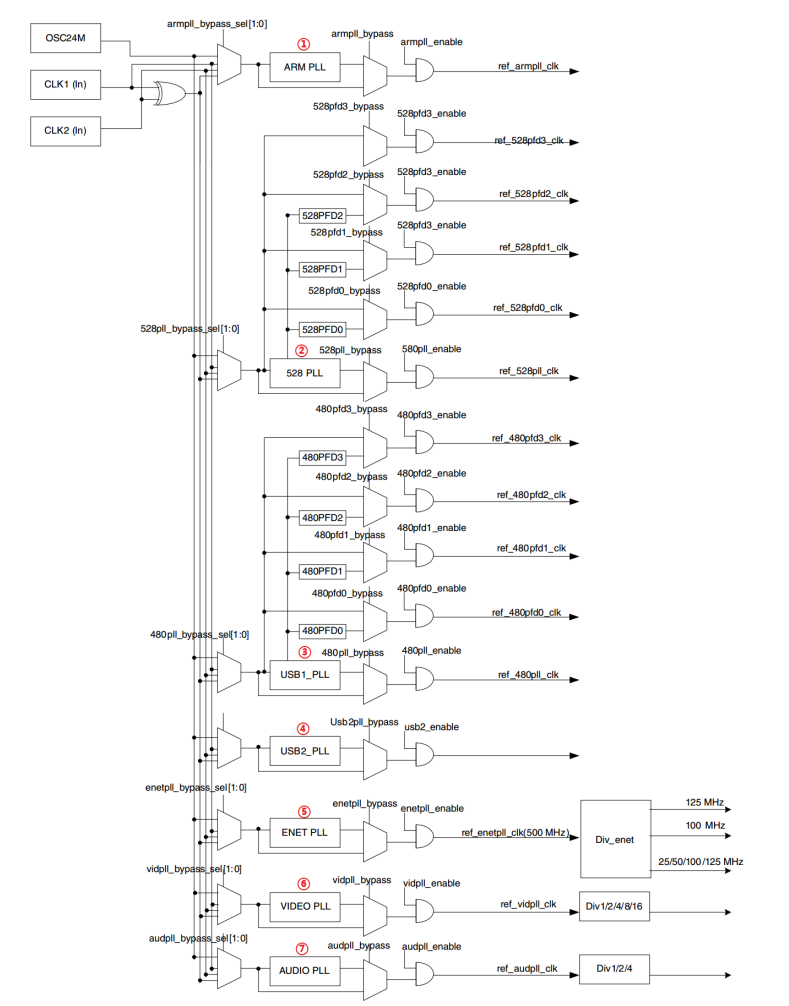

一、第一张图:i.MX6U 时钟树顶层(PLL 与分频输出)

这张图是 i.MX6U 芯片的时钟产生顶层架构,核心是 PLL(锁相环) 和 PFD(分数分频器),把外部 24MHz 晶振(OSC24M)倍频成各种高频时钟源,再分频给不同模块。

1. 输入时钟

- OSC24M:外部 24MHz 晶振,是所有 PLL 的基准时钟。

- CLK1/CLK2:备用外部时钟输入(一般不用)。

2. 主要 PLL 模块(7 个核心 PLL)

| 编号 | PLL 名称 | 作用 | 典型输出频率 |

|---|---|---|---|

| ① | ARM PLL | 专门给 CPU 内核 提供时钟 | 最高 996MHz(可配置) |

| ② | 528 PLL | 通用系统 PLL,输出 528MHz,再通过 528PFD0~3 分频 | 528MHz → 分频后 352~528MHz 范围 |

| ③ | 480 PLL | 通用系统 PLL,输出 480MHz,再通过 480PFD0~3 分频 | 480MHz → 分频后 320~480MHz 范围 |

| ④ | USB1/2 PLL | 专门给 USB 模块 提供 480MHz 时钟 | 480MHz(USB 必须精确 480MHz) |

| ⑤ | ENET PLL | 专门给 以太网模块 提供时钟 | 500MHz → 分频后 100/125MHz 等 |

| ⑥ | VIDEO PLL | 专门给 显示/视频模块 提供时钟 | 可配置频率,支持多种显示分辨率 |

| ⑦ | AUDIO PLL | 专门给 音频模块 提供时钟 | 可配置频率,支持 I²S/SAI 等音频接口 |

3. 关键控制逻辑

- bypass 开关:

armpll_bypass/528pll_bypass等,用于绕过 PLL,直接用 24MHz 时钟(调试或低功耗用)。 - enable 开关:

armpll_enable/528pll_enable等,用于关闭不用的 PLL 以节省功耗。 - PFD 分频:528PLL 和 480PLL 各带 4 组 PFD(分数分频),可以把 528/480MHz 精细分频成不同频率,给不同外设用。

- 最终输出:每个 PLL/PFD 输出一个

ref_xxx_clk,作为第二张图中“时钟根生成器”的输入源。

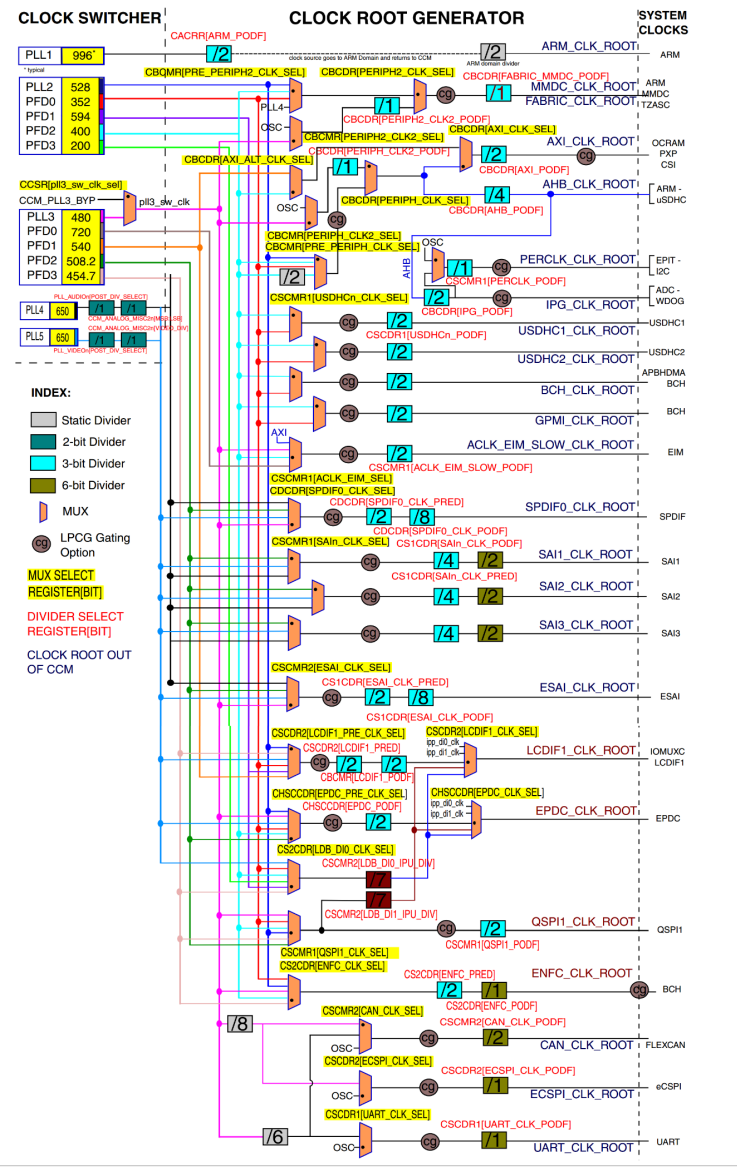

二、第二张图:时钟根生成器(Clock Root Generator)

这张图是 时钟分发层,把第一张图的 PLL/PFD 时钟,通过 MUX(多路选择器)、分频器、门控,最终分配给每个外设模块(如 UART、I2C、SPI、GPIO 等)。

1. 核心组件

- PLL 输入:左侧

PLL1~PLL5对应第一张图的 ARM PLL、528 PLL、480 PLL 等,频率标注如996、528、480等。 - MUX(多路选择器):橙色梯形图标,用于选择时钟源(比如选择 PLL1 还是 PLL2 作为某个模块的时钟)。

- 分频器:

- 灰色:静态分频(固定 1 分频)

- 蓝色:2 分频

- 青色:3 分频

- 绿色:6 分频 用于把高频 PLL 时钟降到外设需要的频率(比如 UART 只需要 80MHz 左右)。

- LPCG Gating:带锁的圆圈,时钟门控,可以单独关闭某个模块的时钟以节省功耗。

- Clock Root Out:右侧

xxx_CLK_ROOT,就是最终给外设模块的时钟,比如UART_CLK_ROOT、SPI_CLK_ROOT、IPG_CLK_ROOT等。

2. 典型模块时钟路径示例(以 UART 为例)

- 时钟源选择:

CSCDR[UART_CLK_SEL]选择时钟源(比如 OSC 24MHz 或 PLL3 分频后的时钟)。 - 分频:

CSCDR[UART_CLK_PRED]+CSCDR[UART_CLK_PODF]两级分频,把高频时钟降到 UART 所需的 80MHz 或 40MHz。 - 门控:

UART_CLK_ROOT经过 LPCG 门控,控制是否给 UART 模块提供时钟。 - 模块使用:UART 模块用此时钟生成波特率,进行串口通信。

3. 关键时钟根说明

- ARM_CLK_ROOT:CPU 内核时钟,来自 ARM PLL,最高 996MHz。

- IPG_CLK_ROOT:外设总线时钟(如 I2C、SPI、UART 等),一般 66MHz 或 80MHz。

- AHB_CLK_ROOT:高速外设总线时钟(如 USB、SDHC、以太网等),一般 132MHz 或 166MHz。

- PERCLK_ROOT:低功耗外设时钟(如 WDOG、GPT 等),一般 32kHz 或 24MHz。

- UART_CLK_ROOT / SPI_CLK_ROOT / SAIn_CLK_ROOT:各外设专用时钟,可独立配置频率。

三、整体时钟工作流程

- 源产生:外部 24MHz 晶振 → 各 PLL 倍频 → 生成 528MHz/480MHz/996MHz 等高频时钟。

- 精细分频:PLL 输出 → PFD 分频 → 生成多种中间频率时钟源。

- 路径选择:中间时钟源 → MUX 选择 → 分频器降频 → 生成

xxx_CLK_ROOT。 - 模块使用:

xxx_CLK_ROOT→ 外设模块 → 门控控制是否开启时钟。

四、开发中的实际意义

- 配置时钟:裸机开发时,需要先配置 PLL 和分频器,给 CPU 和外设提供稳定时钟。

- 功耗控制:通过

bypass、enable、LPCG关闭不用的 PLL 和模块时钟,降低功耗。 - 外设驱动:每个外设驱动都要配置对应的

xxx_CLK_ROOT频率,比如 UART 要根据时钟频率计算波特率,SPI 要根据时钟频率配置分频。 - 性能调节:提高 ARM PLL 频率可以提升 CPU 性能,但会增加功耗;降低外设时钟可以节省功耗,但会降低外设速度。

五、总结

- 第一张图:时钟源层,负责把 24MHz 晶振倍频成各种高频 PLL 时钟。

- 第二张图:时钟分发层,负责把高频时钟分频、选择,最终给每个外设模块提供合适的时钟。

- 两者结合就是 i.MX6U 完整的时钟树,是嵌入式裸机开发中最核心的底层配置,所有外设驱动都依赖正确的时钟配置。

二、时钟核心概念

1. 基础时钟源

- OSC24M:外部 24MHz 晶振,所有 PLL 的基准时钟源,稳定可靠。

- step_clk:临时时钟源,默认来自 OSC24M,用于 PLL 配置时的安全过渡,避免时钟不稳定导致系统崩溃。

2. 核心 PLL 模块

| PLL 名称 | 用途 | 典型输出 | 备注 |

|---|---|---|---|

| PLL1(ARM_PLL) | CPU 内核专用 | 1056MHz(可配置) | 决定 CPU 运算性能,输出后经 CACRR 分频给 CPU |

| PLL2(528PLL) | 系统通用主 PLL | 固定 528MHz | 为大部分外设/总线提供时钟源,带 4 组 PFD 分频 |

| PLL3(480PLL) | 系统通用 PLL | 固定 480MHz | 为 USB、外设等提供时钟源,带 4 组 PFD 分频 |

| PLL4/5(USB/VIDEO/AUDIO) | 专用功能 PLL | 480MHz/可配置 | USB、视频、音频模块专用,保证协议精度 |

3. PFD(分数分频器)

- 依附于 PLL2/PLL3,每个 PLL 带 PFD0~PFD3 共 4 组独立 PFD。

- 作用:将 PLL 固定输出的高频时钟(528MHz/480MHz)精细分数分频,生成多种频率,适配不同外设。

- 公式:

Output = F_PLL × 22 / PFD_FRAC(PFD_FRAC 为分频系数,范围 16~35) - 示例:PLL2=528MHz,PFD0_FRAC=27 →

528×22/27≈352MHz

4. 时钟分发关键组件

- MUX(多路选择器):选择时钟源,如

pll1_sw_clk可选择pll1_main_clk或step_clk。 - 分频器:

- CACRR:CPU 内核专属分频寄存器,

ARM_PODF = 写入值 + 1,如写入 1 → 2 分频。 - 通用分频器:2/3/6 分频,用于总线、外设降频。

- CACRR:CPU 内核专属分频寄存器,

- LPCG(时钟门控):独立开关外设时钟,降低功耗。

- Clock Root:最终给外设的时钟(如

UART_CLK_ROOT、AHB_CLK_ROOT)。

三、PLL1(ARM_PLL)配置流程(CPU 主频 528MHz)

1. 配置步骤

-

判断当前时钟源

if(((CCM->CCSR >> 2) & 0X1) == 0) { ... }- 若

pll1_sw_clk_sel(bit2)=0,表示当前使用pll1_main_clk,需先切换到step_clk。

- 若

-

切换到临时时钟 step_clk

CCM->CCSR &= ~(1 << 8); // step_clk 选择 OSC24M(bit8=0)CCM->CCSR |= (1 << 2); // pll1_sw_clk 切换到 step_clk(bit2=1) -

配置 PLL1 输出 1056MHz

- 公式:

Output = f_ref × DIV_SELECT / 2 - 代入:

1056 = 24 × DIV_SELECT / 2 → DIV_SELECT=88

CCM_ANALOG->PLL_ARM = (1 << 13) | (88 & 0x7F);bit13=1:使能 PLL1;bit0~6=88:设置倍频系数。

- 公式:

-

配置 CPU 分频(CACRR)

CCM->CACRR = 1; // ARM_PODF=1 → 2 分频(1056MHz/2=528MHz) -

切回 PLL1 时钟源

CCM->CCSR &= ~(1 << 2); // pll1_sw_clk 切换回 pll1_main_clk(bit2=0)

2. 关键寄存器总结

| 寄存器 | 作用 | 关键位 |

|---|---|---|

CCM->CCSR | 时钟控制/状态 | bit2:pll1_sw_clk_sel;bit8:step_clk_sel |

CCM_ANALOG->PLL_ARM | PLL1 配置 | bit13:PLL 使能;bit0~6:DIV_SELECT(倍频系数) |

CCM->CACRR | CPU 分频 | ARM_PODF(0 |

四、PLL2/PLL3 及 PFD 配置

1. PLL2(528MHz)固定配置

- PLL2 为系统主 PLL,固定输出 528MHz,一般不修改倍频系数。

- 寄存器:

CCM_ANALOG->PLL_SYS(默认配置即可)。

2. PLL2_PFD0~PFD3 配置

- 寄存器:

CCM_ANALOG->PFD_528 - 每路 PFD 对应独立分频位(6 位),设置

PFDx_FRAC即可。 - 示例:PLL2_PFD0 输出 352MHz

// PFD0_FRAC=27 → 528×22/27≈352MHzCCM_ANALOG->PFD_528 &= ~(0x3F << 0); // 清除 PFD0 位CCM_ANALOG->PFD_528 |= (27 << 0); // 设置 PFD0_FRAC=27

3. PLL3(480MHz)及 PFD 配置

- PLL3 固定输出 480MHz,寄存器:

CCM_ANALOG->PLL_USB1 - PFD 配置同 PLL2,寄存器:

CCM_ANALOG->PFD_480,公式:Output = 480 × 22 / PFD_FRAC

五、时钟树整体工作流程

- 源产生:OSC24M → PLL 倍频 → 生成 1056/528/480MHz 等高频时钟。

- 精细分频:PLL 输出 → PFD 分数分频 → 生成多组中间频率。

- 路径选择:MUX 选择时钟源 → 分频器降频 → 生成

xxx_CLK_ROOT。 - 模块使用:

xxx_CLK_ROOT→ 外设模块 → LPCG 门控控制时钟开关。

六、开发关键注意事项

- PLL 配置安全规范:修改 PLL 前必须切换到

step_clk(24MHz),避免时钟不稳定导致死机。 - 分频与倍频的关系:

- PLL1 是生频(24MHz → 1056MHz),CACRR 是降频(1056MHz → 528MHz),二者共同决定 CPU 主频。

- 不直接将 PLL1 设为 528MHz:高倍频下时钟稳定性更好,且预留扩展空间。

- 功耗控制:通过

PLL enable/bypass、LPCG关闭不用的时钟,降低功耗。 - 外设时钟依赖:所有外设驱动必须先配置

xxx_CLK_ROOT频率,再初始化寄存器(如 UART 波特率计算)。

Some information may be outdated